【導(dǎo)讀】互連中的信號完整性損耗對于數(shù)千兆赫茲高度復(fù)雜的SoC來說是非常關(guān)鍵的問題,因此經(jīng)常在設(shè)計和測試中采用一些特殊的方法來解決這樣的問題。本文介紹如何利用片上機制拓展JTAG標準使其包含互連的信號完整性測試,從而利用JTAG邊界掃描架構(gòu)測試高速系統(tǒng)級芯片(SoC)的互連上發(fā)生的時延破壞。

互連中的信號完整性損耗對于數(shù)千兆赫茲高度復(fù)雜的SoC來說是非常關(guān)鍵的問題,因此經(jīng)常在設(shè)計和測試中采用一些特殊的方法來解決這樣的問題。我們認為,完整性損耗(本文有時也稱為完整性故障)是在電壓失真(噪聲)和時延破壞(偏移)超過能接受的門限時發(fā)生的。這樣的門限取決于制造所采用的工藝技術(shù)。這種故障情況的發(fā)生有著許多不可預(yù)料的原因,包括:1. 產(chǎn)生寄生值,例如晶體管尺寸、跨導(dǎo)、門限電壓、寄生電阻/電感/電容值等等的工藝變化,以及傳輸線效應(yīng),例如串擾、過沖、反射,電磁干擾等,這些問題都很難分析而且制造過程中會有變化的互連間耦合效應(yīng)(如耦合電容和互感)。2. SoC中開關(guān)同時切換引起的地線反彈,通常會造成噪聲余量的變化。

完整性故障模型

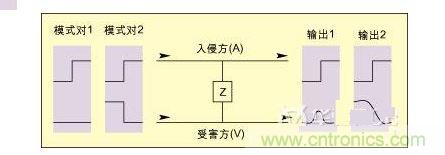

最被廣泛使用的模型是最大入侵方(MA)故障模型,這是許多研究人員用來對長距離互連進行串擾分析和測試的一個簡化模型。如圖1所示,該模型假設(shè)在V(受害方)線上傳輸?shù)男盘枙艿皆诹硗庖粭l相鄰的A(入侵方)線上的信號/變化的影響。這種耦合影響可以用一般的耦合元件Z來概 括。一般來說這種影響的后果是噪聲(引起振鈴和功能錯誤)和時延(引起性能降級)。

本文使用了相同的模型。然而我們需要強調(diào)的是,對何種模式會造成最大的完整性損耗仍有爭論。顯然傳統(tǒng)的MA模型只考慮了電容耦(couplingC),所有的入侵方同時作相同的跳變,而受害方或保持不變(針對最大的振鈴),或作出相反的跳變(針對最大的時延)。當互感起作用時,一些研究人員利用其它方式(偽隨機或恒定)產(chǎn)生測試模式來形成最大的完整性損耗。雖然我們?nèi)允褂肕A模型,但測試方法并不取決于測試模式。在本文中假設(shè)測試模式已被確定,讀者可以看到它們是如何通過增強的JTAG架構(gòu)高效地饋入互連的。

完整性損耗傳感器(ILS)單元

由于千兆赫茲芯片中的完整性損耗已受到越來越多人的重視,一些研究人員開發(fā)出了系列片上傳感器。許多這樣的完整性損耗傳感器(ILS)的基礎(chǔ)都是放大器電路,它能夠檢查出電壓破壞和時延門限。采用D觸發(fā)器的BIST(內(nèi)置自檢)結(jié)構(gòu)被推薦用于運放傳播時延偏差的檢測。在測試模式期間,待測試的運放或被放置于電壓跟隨器配置中以檢測斜率偏差,或被置于比較器配置中以檢測信號傳播時延偏差。

采用IDDT和邊界掃描方法是解決總線互連缺陷的一種測試技術(shù)示。在本例中一個內(nèi)置傳感器被集成進了系統(tǒng)中。該傳感器是一個片上電流鏡像,可以將散亂的電荷轉(zhuǎn)換成相關(guān)的測試時間。噪聲檢測器(ND)和偏移檢測器(SD)單元都是基于改進的串耦PMOS差分傳感放大器,因此價格十分便宜。這些單元緊鄰互連的端末,對實際信號和噪聲進行取樣。每當噪聲或偏移高于可接受的限值時,這些單元就產(chǎn)生1到0的跳變,并存儲于觸發(fā)器中,以便于進一步分析。

有人提供了一個價格較高但更精確的電路,可以皮秒級測試抖動和偏移,這種被稱為EDTC的電路以免打擾方式取樣信號,并通過低速串行信息發(fā)出測試信息。當成本不成問題時,精確信號監(jiān)視概念就能被研究人員所接受,甚至會產(chǎn)生片上示波器的想法。

[page]

ILS單元

雖然任何ILS傳感器都能用于完整性損耗檢測,但為了簡單、經(jīng)濟和實驗的目的,我們還開發(fā)了自己的ILS單元。下面將簡要介紹這種單元的電路和功能,但這種單元的詳細功能不在本文討論范圍。

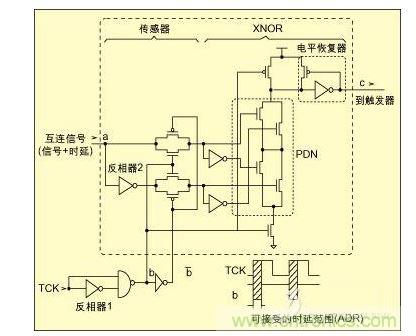

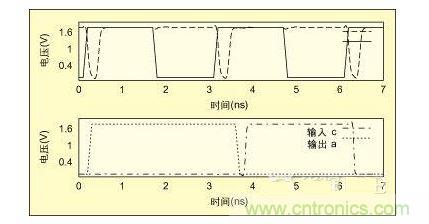

本例所用的ILS是如圖2所示的時延破壞傳感器??山邮艿臅r延范圍(ADR)被定義為觸發(fā)時鐘沿開始的一段時間,所有輸出跳變必須在這段時間內(nèi)發(fā)生。測試時鐘用于創(chuàng)建窗口,以確定可接受的偏移范圍。如果輸入信號a的跳變發(fā)生在b為邏輯’0’的時間內(nèi),那么信號a就在可接受的時 延范圍內(nèi)。任何在b為邏輯’1’的時間內(nèi)發(fā)生的跳變均經(jīng)過傳輸門傳遞給XNOR門,這是利用動態(tài)預(yù)充電邏輯實現(xiàn)的。根據(jù)合理的時延范圍調(diào)整反向器1。在b 為1的時間內(nèi)有信號跳變時輸出c就為1,直到b變?yōu)?,開始下一個預(yù)充電循環(huán)周期。輸出用來觸發(fā)一個觸發(fā)器。圖3所示為輸入信號a有2個信號跳變的單元 SPICE仿真,采用0.18μm技術(shù)實現(xiàn)。第1個信號跳變發(fā)生在0.2ns處,當時b為0,輸出保持為0。第2個信號跳變發(fā)生在3.5ns處,此時b為1,由于超出了可接受的時延周期,輸出c保持為1直到b變?yōu)?。時延傳感器還能檢測到由串話引起的跳變錯誤。脈沖可以被反饋到觸發(fā)器以存儲時延發(fā)生事件,供以后進一步閱讀/分析。

增強的邊界掃描單元

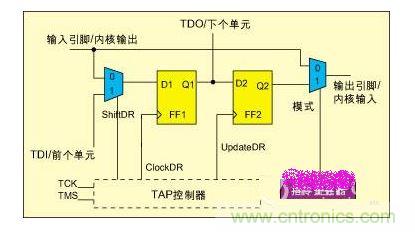

邊界掃描是一種被廣泛使用的測試技術(shù),它要求在輸入或輸出引腳和內(nèi)部內(nèi)核邏輯之間配置邊界掃描單元。邊界掃描測試技術(shù)能夠高效地測試內(nèi)核邏輯和互連。圖4給出了傳統(tǒng)帶移位和更新節(jié)點的標準邊界掃描單元(BSC)。Mode_1使單元處于測試模式。在掃描操作中數(shù)據(jù)通過移位寄存器(Shift-DR狀態(tài))進行移位 。通過掃描輸入端口(TDI)被掃描進邊界掃描單元的測試模式在Update-DR狀態(tài)(UpdateDR信號)下得到并行使用。連接于內(nèi)部邏輯和輸出引 腳之間的邊界掃描單元可以并行捕獲電路響應(yīng),并通過掃描輸出端口(TDO)掃描輸出。利用JTAG標準(IEEE 1149.1)可以測試互連的粘連、開路和短路等故障情況,這是通過“EXTEST”指令實現(xiàn)的,在該指令操作下TAP控制器利用BSC從互連中分離出內(nèi) 核邏輯。但這種測試的目的并不是測試互連的信號完整性。為了測試互連的信號完整性,需要對標準架構(gòu)作少許的改進。

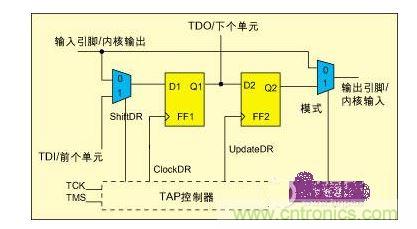

監(jiān)視BSC(OBSC)

建議在互連的接收側(cè)放置一個新的使用ILS單元的BSC,如圖5所示,這種新的BSC被稱為監(jiān)視BSC(OBSC)。ILS被加在接收側(cè)單元,它們能夠捕獲互連末端上帶噪聲和時延的信號。如果它接收到具有完整性問題(如時延破壞)的信號,它會在輸出端輸出一個脈沖,并將觸發(fā)器置為“1”。OBSC有2種工作模式:

1) 完整性模式(SI=1):選擇信號F。在每個Shift-DR狀態(tài)通過掃描鏈輸出被捕獲的完整性數(shù)據(jù),并用于最終的評估。

2) 正常模式(SI=0):在這種模式中ILS被隔離,每個OBSC被當作標準BSC使用。

在掃描輸出過程中,我們需要捕獲輸出F信號并送至FF1。在本例中sel應(yīng)置為0,因此SI和ShiftDR應(yīng)分別為1和 0。當掃描輸出過程開始后,D1被傳送到Q1,并用作下一個單元的TDI。信號完整性信息被捕獲進FF1后ILS觸發(fā)器復(fù)位。在將F值送至Q1后,必須格式化掃描鏈。在本例的Shift-DR狀態(tài)期間,TDI輸入必須連接至FF1。因此必須將sel置為1(SI=’1’,ShiftDR=’1’)從而隔離出ILS路徑。如圖5所示,SI和ShiftDR需要進行或操作,以選擇和發(fā)送信號F到D1,并生成掃描輸出用的掃描鏈。

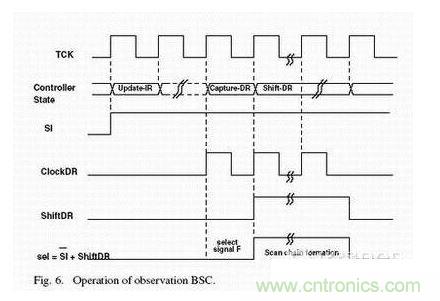

圖6顯示了sel與SI和ShiftDR間的從屬關(guān)系。如圖所示,在Capture-DR狀態(tài),信號F被選中,掃描鏈在 Shift-DR狀態(tài)得到格式化,并根據(jù)被測試的線數(shù)掃描輸出數(shù)據(jù)。表1給出了信號sel的真值表。只有一個控制信號(即SI)是由新指令生成的。執(zhí)行信號完整性信息的監(jiān)視有三種方法:1)應(yīng)用每個測試模式后讀出;2)應(yīng)用測試模式子集后讀出;3)應(yīng)用整個測試模式后一次性讀出。具體選擇哪種方法取決于可接受的時間開銷。第1種方法非常耗時,但它可以盡可能詳細地顯示每個互連的完整性信息。第3種方法速度非常快,但完整性信息比較少,因為只能得到哪個模式或哪個模式子集引起完整性故障的信息,無法獲知故障類型。方法2可以幫助用戶在測試時間和準確性之間取得平衡。

[page]

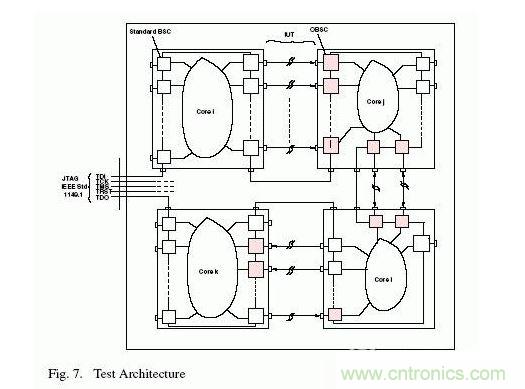

測試架構(gòu)

圖7給出了針對小型SoC的整體測試架構(gòu),其中的JTAG輸入(TDI、TCK、TMS、TRST和TDO)使用時沒加任何修改。但定義了一條新的指令,主要用于信號完整性測試中讀取測試結(jié)果。從圖7可以看到,只是每個互連的接收端單元改成了OBSC。對于雙向互連,OBSC 單元用于Core j和Core1之間的雙側(cè)。其它單元都是標準BSC,在信號完整性測試模式期間出現(xiàn)在掃描鏈中。ILS的作用是獨立的,不需要特殊的控制電路來控制這類單元的時序。由F顯示的完整性信息被掃描輸出,用以確定有問題的互連。

1. EX-SITEST指令

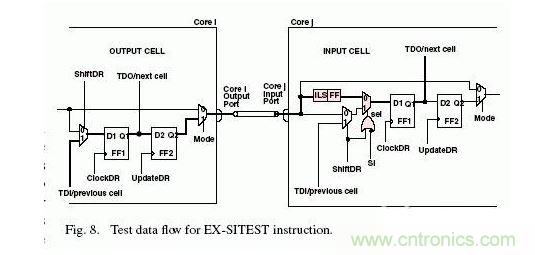

針對新的測試架構(gòu),建議在IEEE 1149.1指令集中增加一條新的指令EX-SITEST。這條指令類似于EXTEST指令,但增加了控制信號SI。在Update-IR狀態(tài),這條指令被解碼并產(chǎn)生(SI_1)。此時輸出單元用作標準BSC,而輸入單元用作OBSC。信號F在Capture-DR狀態(tài)時被捕獲,并在Shift-DR狀態(tài)期間以每個時鐘周期的速度向外移位輸出。本例中TAP控制器狀態(tài)不會改變,但在指令解碼時需要一些變化。存在于內(nèi)核之間的EX-SITEST指令的數(shù)據(jù)流如圖8所示。

2. 測試過程

首先通過EX-SITEST指令裝載TAP控制器IR,然后將所有的測試模式應(yīng)用到互連上,同時ILS單元捕獲互連末端的信號,并檢測所有可能的故障。在測試應(yīng)用過程結(jié)束后,必須讀取存儲于ILS單元FF的結(jié)果。監(jiān)視過程可以利用3種方法之一。比如使用方法3,應(yīng)用所有測試模式,然后一次性讀出完整性信息。

3. 測試數(shù)據(jù)壓縮

在傳統(tǒng)的邊界掃描架構(gòu)(BSA)中,測試模式是一個一個掃描進來并應(yīng)用到互連上。舉例來說,采用最大入侵方(MA)故障模型 的n位互連中,12個測試模式被應(yīng)用到每個受害線,在將測試模式應(yīng)用到受害線上時要求12n 時鐘。在n個互連間翻轉(zhuǎn)受害線,總的時鐘數(shù)量(測試應(yīng)用次數(shù))是12n2。當然,MA是一個簡化模型。如果采用更復(fù)雜的模型或SoC中具有大量互連時,測試模式數(shù)量會激增,此時壓縮就顯得很有必要了。本文介紹一種針對增加邊界掃描架構(gòu)的簡單有效的壓縮技術(shù)。由于空間有限,本文只能作一簡要介紹,以此說明增 加型JTAG架構(gòu)的靈活性。

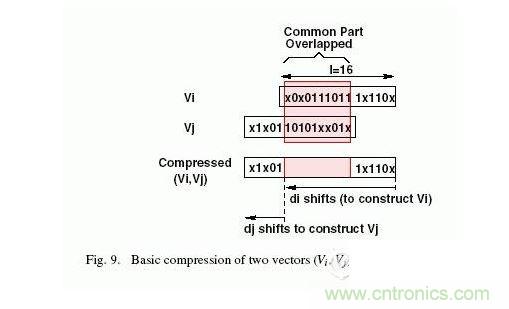

這種壓縮技術(shù)有二個關(guān)鍵點。首先,我們的方法是一個簡捷的無損壓縮法,通過確定相鄰二個模式間的最大相似性并覆蓋它們來構(gòu)筑壓縮位流。其次,由于這種壓縮法即無破壞性也不對模式重新排序,因此不需要額外的解壓縮硬件。而且僅是利用自動測試設(shè)備(ATE)通過控制JTAG TMS控制輸入端執(zhí)行解壓縮過程。當測試模式產(chǎn)生后,常會有大量無關(guān)緊要的模式出現(xiàn)在測試模式集中。針對信號完整性產(chǎn)生的模式也是這樣,特別是在考慮了地區(qū)度量標準時(限制開發(fā)模式空間)更是如此。在任何情況下我們都假設(shè)測試集由相同長度的包含不重要的模式組成。圖9表達了我們的基本壓縮想法,即充分利用不重要的部分覆蓋盡可能多的位來完成2個模式Vi和Vj(長度是1_16)的壓縮。

本文小結(jié)

在本例中,壓縮后的數(shù)據(jù)(Vi,Vj)掃描輸入時只需要21個時鐘,而未壓縮的數(shù)據(jù)需要16+16=32個時鐘。需要注意的是,為了解壓縮指定的數(shù)據(jù)流,我們需要一個模式一個數(shù)字(如本例中的di和dj)才能構(gòu)造(解壓縮)模式?;谶吔鐠呙铚y試的目的,這些數(shù)量就是更新 BSC單元內(nèi)容前要求的移位(即時鐘)數(shù)量。我們假設(shè)ATE存儲著解壓縮數(shù)據(jù)(d值如0≤d≤1),在掃描輸入位流時,該數(shù)據(jù)會在d個時鐘后激活TMS (測試模式選擇)信號。然后TMS信號促使TAP控制器產(chǎn)生用于信號完整性測試的正確控制指令(如EX-SITEST)。因此在我們的架構(gòu)中不需要額外的解壓縮硬件。